面板級封裝取代CoWoS? 專家:3-5年難改變

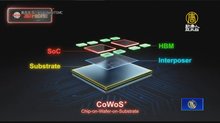

【新唐人亞太台 2024 年 06 月 27 日訊】CoWoS先進封裝產能吃緊,輝達(NVIDIA)的GB200,傳出提早導入面板級扇出型封裝,也有日本媒體報導,台積電有意投入研發,不過南韓三星對外表示,自家在面板級封裝,技術領先台積電,我們請教寬量國際顧問何柏杰怎麼觀察,兩大技術發展走向?面板級封裝是否可能挑戰,台積電既有CoWoS競爭優勢?

寬量國際顧問 何柏杰:「

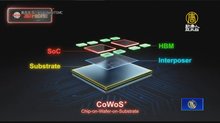

好的,我想因為AI的需求,各種不同半導體的技術,又再次被擺上檯面來做比較,那近期的FOPLP面板級扇出型封裝,跟台積電既有的CoWos,Chip on Wafer on Substrate,這兩個技術就是被拿來做個比較。

那其實對我來說,目前以AI的晶片供不應求的情況來看,目前AI晶片對於先進封裝的技術,是以CoWos為最優先,也是目前產能最不夠的一個瓶頸,那台積電在最近也開始準備繼續擴這個CoWos的產能,那就AI的封裝技術來看,我認為要考量技術的移轉,必須要從一個整個這個Total Cost of Ownership來看,整段製程的完成到底是用最有效率,最良率最高的技術來進行才是最有效率的。

那所以目前看起來,以AI的晶片在前段時間,就是用原型的Wafer(晶圓),12寸晶圓在製造的這個過程中,它用CoWos來搭配,這會是一個最完美的組合,顧及良率、顧及這個晶片的效能,還有在AI趨勢下面,所有這些大模型的AI,它的Die Size(晶片尺寸)越做越大的情況下,要輕易的去更換基板的這個面板及封裝的這個技術,對成本來說是沒有辦法考量的,沒辦法去接受的。

那在各家公司的RD的roadmap發展路徑裡面,我想FOPLP面板級封裝確實會是一個未來的選項,那這個事情要發生,我覺得可能至少要三到五年後,最有可能出生的發生的地方反而是研發,每一家公司在研發的過程中,可能會視為說,它的晶片如果是Size比較小的。

它可以先試用這個來做,但以目前來看這個趨勢,我是覺得FOPLP(Fan-Out Panel-Level Packaging),通常就是在做面板的公司,它為了要拿到AI的商機,它當然是對我來說說,我這個可以試用在AI晶片的風格上。

那我覺得面板級封裝還是有它的市場,但它的市場並不是AI,而是這些電源、車用、高壓的這些IC,但是Size稍微小一點,那用的比較是成熟製程,以當你前段用的是成熟製程,你後段當然就有一些空間,有一些這個犯錯空間去採用新技術,讓整個效率提高,那去抵銷可能你後段的這個封裝會出錯了這個成本。

所以以這個角度來看,我想AI的應用還是會以CoWos來做,封裝為主,那麼傳統的一些成熟製程的產品,才會採用FOPLP的這個技術,我想這樣的局面,應該在未來三到五年,不會有太大的改變。'」

相關新聞

-

台積電傳研發新技術 從晶圓級轉向面板級封裝

2024-06-20 17:16:18產業消息繼續看到,台積電正投入下世代封裝技術,日經新聞報導引述不具名人士說法,[切台積電正在研發新的先進晶片封裝技術,可能從晶圓級,轉向面板級封裝,利用矩形面板封裝,取代目前所採用的傳統圓形晶圓,這項技術可以在一片晶圓上放置更多晶片組,以因應未來的AI需求趨勢。台積電對此表示,公司密切觀察先進封裝的進展與發展,包括面板級封裝在內。

-

台積電嘉義CoWos廠挖到遺跡 南科:影響不大

2024-06-17 17:10:53來關心,台積電在嘉義科學園區,建置先進封裝產能,增設兩座CoWoS廠,第1座封裝廠,5月開始動工,不過近日疑似挖到遺跡,依照文化資產保存法規定,現場已經暫停施工。南科管理局證實,已經接獲台積電提出先蓋第2座CoWos廠的計畫,並強調會全力提供協助。根據了解,台積電除了提出2場興建計畫申請,也會透過調整施工動線、工序等方式來因應,根據南科管理局評估,第1座封測廠停工期不會太久,第2座廠的目標時程不會有太大影響。

-

挖到遺跡!台積電嘉義廠停工 南科:影響不大

2024-06-17 19:21:46來關心,台積電在嘉義科學園區,建置先進封裝產能,增設兩座CoWoS廠,第1座封裝廠5月動工,不過近日疑似挖到遺跡,依據文化資產保存法,現場暫停施工。南科管理局證實,已接獲台積電提出,先興建第2座CoWoS廠的計畫。根據了解,台積電也會透過調整施工動線、工序等方式來因應,根據南科管理局評估,第1座封測廠的停工期不會太久,第2座廠的目標時程,不會有太大影響。

-

屏東蓋CoWoS廠?台積電加速南台灣布局

2024-06-29 14:33:55台積電CoWoS先進封裝產能供不應求,有消息傳出,台積電有意前往屏東縣,興建先進封裝廠,對此,台積電回應,以台灣作為主要基地,不排除任何可能性。

-

台積電CoWoS先進封裝新廠 落腳嘉義

2024-03-23 14:43:04好,再來看到,台積電則是持續在台灣布局擴產,兩座CoWoS先進封裝廠,確定落腳嘉義科學園區,預計今年5月動工,2026年量產。

-

台積電先進封裝落腳嘉義 傳賴清德今訪台積

2024-03-19 07:35:24產業焦點,CoWoS產能供不應求,台積電拍板,兩座CoWoS先進封裝廠,確定落腳嘉義科學園區,預計今年5月動工,2026年量產。

-

台積電傳2百億買群創南科四廠 擴充先進封裝

2024-08-12 17:32:21再來關心,面板大廠群創的南科四廠出售案,傳出將由台積電以總價上看2百億元、比底價高兩成的金額買下,未來將用於擴充先進封裝,或是後續先進製程生產使用。對此,台積電表示,不對市場傳言作出評論,不過業界認為,消息有望最快在台積電13日的董事會後公告。

-

台積電買下群創廠房!試驗開發面板級封裝?

2024-08-16 19:15:48好,晶圓代工龍頭台積電,正式宣布以171億元買下群創南科四廠,我們請教資深半導體產業分析師柴煥欣,外傳台積電此次購廠,與先進封裝布局有關,魏哲家在法說會上,也曾提到扇出型面板級封裝,未來除了先進製程外,顯然後端的封裝,對台積電更為要,未來台積電在台灣的產能、供應鏈布局,您怎麼觀察?

-

台積電再下一城!熊本二廠後 封裝廠可能性高

2024-04-16 17:20:49市場傳出,台積電啟動在日本興建第二座晶圓廠之後,可能也將選定日本設立第一座先進封裝廠,我們請教寬量國際顧問何柏杰,您怎麼觀察,台積電先進封裝落地日本的可能性?這是否將有助穩固台積電先進封裝領導地位?

-

台積電加速南台灣布局 傳屏東蓋CoWoS廠

2024-06-26 19:20:34台積電逐步在南台灣,擴大先進製程產能。24日,高雄市政府宣布,台積電P3廠用地通過環評,可開始動工。另外,面對CoWoS產能供不應求,有消息傳出,台積電有意前往屏東,再建先進封裝廠。

-

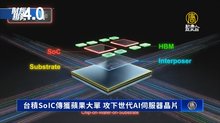

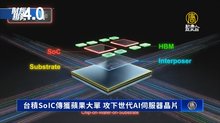

不只CoWoS被瘋搶!台積電SoIC傳首獲蘋果大單

2024-07-04 19:23:46台積電不只CoWoS產能被國際大廠瘋搶,現在更傳出,先進封裝技術SoIC,將首度被蘋果採用,目標明年下半年大量生產。專家研判,台積電擴充SoIC產能指日可待,甚至是現在進行式。相關消息也將成為台積電18日法說會,市場關注的一大焦點。

-

光靠AI業務!外媒:台積將碾壓英特爾代工收入

2024-04-22 19:17:45全球晶圓代工版圖,龍頭台積電持續領先。外媒預估,2030年,台積電的收入有望達1千8百億美元,光是AI業務規模的460億美元,就遠超過美商英特爾所有的代工收入。

-

台積電接單強強滾 南韓HBM晶片對台出口暴增

2024-08-12 19:23:09好,今年上半年,美國晶片大廠輝達的AI晶片持續供不應求,進而使台灣成為南韓記憶體晶片第3大出口市場,超越越南和美國。根據韓媒報導,南韓上半年記憶體晶片對台灣的出口金額,來到42.6億美元,較去年同期成長225%,超過兩倍之多。主要原因是晶片大廠SK海力士,為大客戶輝達生產的高頻寬記憶體HBM晶片,大量出口台積電進行封裝。

-

台積電、美光買面板廠房 牽動半導體新佈局

2024-08-31 14:03:12近期半導體業界,還有兩大指標事件,面板雙虎群創、友達,8月出售旗下廠房進行活化土地資產,而買家則分別是台積電、記憶體大廠美光,業界認為兩項交易將牽動全球封測產業版圖、晶圓代工布局。

-

CoWoS需求熱!台積電先進封裝新廠進駐嘉義

2024-03-18 21:41:12產業焦點,CoWoS產能供不應求,台積電拍板,兩座CoWoS先進封裝廠,確定落腳嘉義科學園區,預計今年5月動工,2026年量產。

-

台積SoIC傳獲蘋果大單 攻下世代AI伺服器晶片

2024-07-06 14:27:51再來看到,台積電不只CoWoS產能被國際大廠瘋搶,現在更傳出,先進封裝技術SoIC,將首度被蘋果採用,目標明年下半年 大量生產。

-

台積高雄環評通過可動工!傳屏東蓋CoWoS廠

2024-06-26 17:18:36台積電逐步在南台灣,擴大先進製程產能。24日,高雄市政府宣布,台積電P3廠用地通過環評,可開始動工。另外,面對CoWoS產能供不應求,有消息傳出,台積電有意前往屏東,再建先進封裝廠。

-

半導體封裝戰 韓廠憂10年後韓國封裝從市場消失

2024-09-05 17:27:24AI浪潮帶動高算力需求,透過先進封裝技術提升晶片效能,成為半導體業新顯學。數據指出,去年全球封裝市場,南韓市占率4.3%,遠遠落後龍頭台灣的46.2%,韓媒報導引述韓國半導體設備業者說法,儘管韓國HBM表現良好,但用於AI半導體的先進封裝都在台灣進行,韓國半導體設備材料業者憂心,再過十年韓國封裝將從市場上消失。

-

不只CoWoS被瘋搶!台積電SoIC傳首獲蘋果採用

2024-07-04 17:35:16台積電不只CoWoS產能被國際大廠瘋搶,現在更傳出,先進封裝技術SoIC,將首度被蘋果採用,目標明年下半年大量生產。專家研判,台積電擴充SoIC產能指日可待,甚至是現在進行式。相關消息也將成為台積電18日法說會,市場關注的一大焦點。

-

傳台積CoWoS技術考慮赴日 專家:規模應有限

2024-03-18 17:15:12目前台積電所有的CoWoS產能都在台灣,不過在產能需求強勁下,市場傳出,台積電考慮在日本建立先進封裝產能。根據路透社18日引述消息人士指出,台積電目前考慮將CoWoS先進封裝技術引入日本,但相關審議工作仍處於早期階段。對此,TrendForce分析師認為,就算台積真的要在日本建立先進封裝產能,規模應該有限。

財經趨勢4.0

財經趨勢4.0 新聞大破解

新聞大破解 新唐人財經新聞

新唐人財經新聞 選戰大透視

選戰大透視 遇見新聞

遇見新聞 美國思想領袖

美國思想領袖 老外看中國、老外看台灣

老外看中國、老外看台灣 美麗心台灣

美麗心台灣 田美女奉茶實客

田美女奉茶實客 廚娘香Q秀

廚娘香Q秀 大千世界

大千世界 1000步的繽紛台灣

1000步的繽紛台灣 好樣!Formosa

好樣!Formosa 健康1+1

健康1+1 談古論今話中醫

談古論今話中醫 我的音樂想想

我的音樂想想 胡乃文開講

胡乃文開講 她健康She Health

她健康She Health 天庭小子-小乾坤

天庭小子-小乾坤 總統教育獎

總統教育獎 全國孝行獎

全國孝行獎 健談交流

健談交流 悠遊字在

悠遊字在 傳奇時代

傳奇時代 音樂大賽特別節目

音樂大賽特別節目